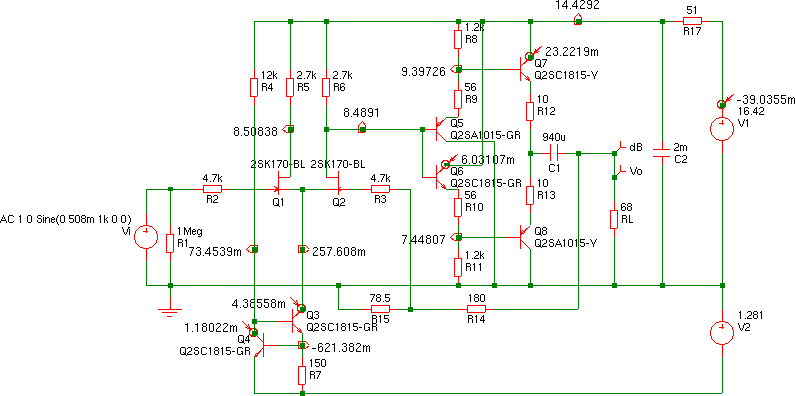

回路は,ぺるけさんの原回路(http://www2.famille.ne.jp/˜teddy/pre/pre6.htm)と全く同じです(図16).

出力コンデンサは940

ケースはタカチのHEN110420にしました. 電源トランスは,ノグチトランスのPM18X02を使いました. トランスと増幅部の距離が取れないので, 念のためにショートリングを付けました.

電源部はユニバーサル基板に組みましたが, 横着をしてサイズを切りつめなかったため, ピンジャックと干渉して取付が困難となり, 3本のネジで固定しています. 写真では電源部のパワートランジスタに放熱器が付いていませんが, 動作時にかなり熱くなるため,小型の放熱器を取り付けました.

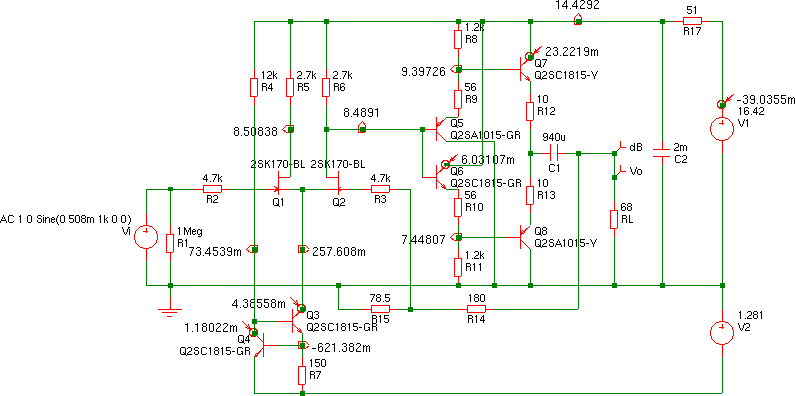

無帰還時のゲインは,25.9dB (19.7倍)です.

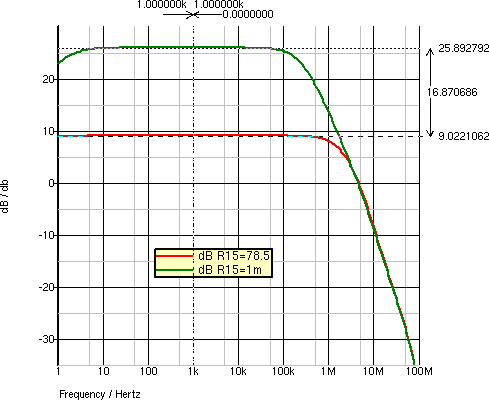

負荷抵抗を変化させた場合の周波数特性を 図20に示します.

RL = 15 Ωの低域のカットオフ周波数は,2Hz程度です.

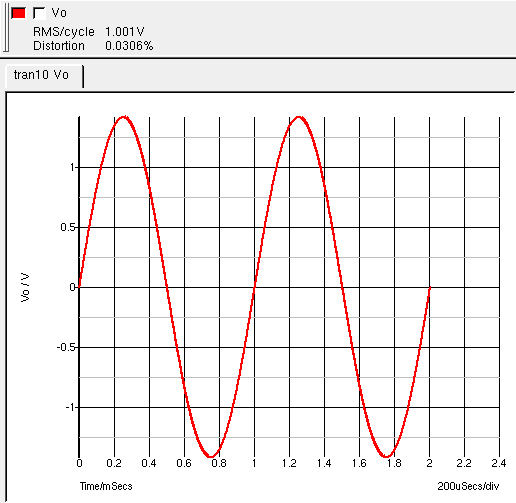

68Ωの負荷に1V出力時の波形を図21に示します.

歪率は,0.0306%です.

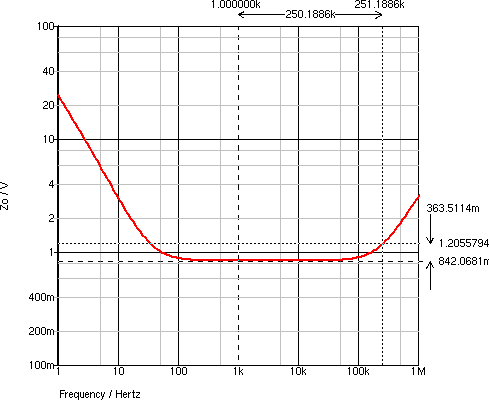

出力インピーダンスの特性を図22に示します.

中域の出力インピーダンスは,0.84Ωです.

負荷開放時の出力電圧対歪率特性を図23に示します.

無帰還時の特性は,後述のマイナス電源の改造後のものです.負荷抵抗の違いによる出力電圧対歪率特性を図24に示します.

この回路の場合,アイドル電流が実測で約31mAですから, 実効値で22mAまでA級動作します. その時の出力電圧は,| 負荷(Ω) | 15 | 22 | 33 | 47 | 68 |

| 出力電圧(V) | 0.329 | 0.482 | 0.723 | 1.03 | 1.49 |

負荷抵抗の違いによる出力電力対歪率特性を図25に示します.

負荷抵抗の違いによる周波数特性を図26に示します.

無帰還時のゲインは20.2倍(26.1dB)で,負帰還量は17.1dBです.出力インピーダンスの周波数特性を図27に示します.

中域における出力インピーダンスは,約0.8Ωです.1V出力時のクロストーク特性を図28に示します.

低域は測定限界以下であり,高域も問題ありません.残留雑音は,以下の通りです.

| チャネル | 600kHz | 80kHz | 30kHz | A特性 |

| L | 27.5 |

13.0 |

10.2 |

4.2 |

| R | 26.6 |

10.6 |

6.8 |

4.0 |

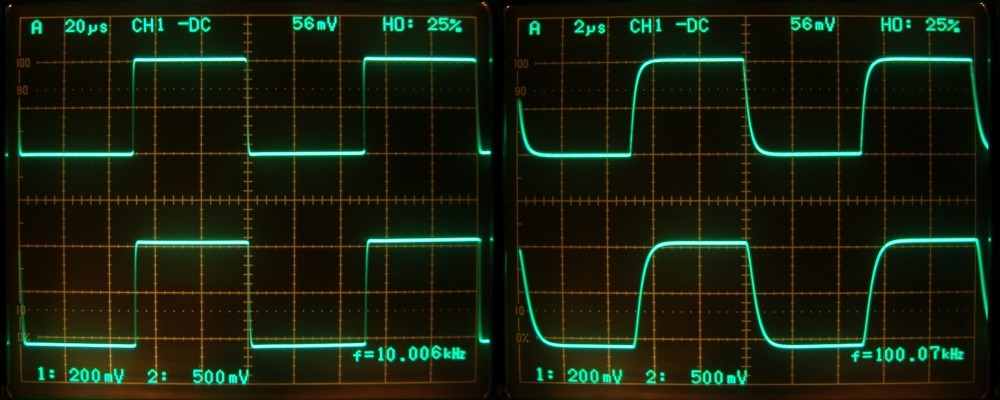

68Ωを負荷にしたときの方形波応答を, 図29に示します.

歪みは差動段で発生しています.

負帰還が入力の逆側に掛かっているので,

負帰還の量が多いと,大きな同相入力が加わり,

定電流回路が正しく動作しなくなります.

Q3のエミッタは,Q4の VBE (約0.62V)だけマイナス電源より高く,

それにQ3の飽和電圧(約0.2V)を加えた0.8Vが,

回路が正常に働くのに必要な電圧になります.

私がマイナス電源用に使用したダイオード1N4007 2本では,

マイナス電圧が約-1.28Vであり,

初段のFETのバイアスが-0.26Vなので,

同相入力範囲は

1.28 + 0.26 - 0.8 = 0.74Vが限界となります.

したがって,入力電圧が

0.74/![]() = 0.52Vを超えると

歪みが発生します.

= 0.52Vを超えると

歪みが発生します.

差動段の出力側,および出力段にはまだ余裕がありますから, マイナス電源を高くすれば,この問題を回避できます. ダイオード1本あたりの電圧を高くするため, 小信号用のダイオード1N4148に変更し,4本直列で使用しました.

改造後の負荷抵抗の違いによる出力電圧対歪率特性を図30に示します.

負荷開放では3Vを超える出力が得られています.改造後の負荷抵抗の違いによる出力電力対歪率特性を図31に示します.

すべての負荷抵抗において,100mWの出力が1%以下の歪みで得られています.