|

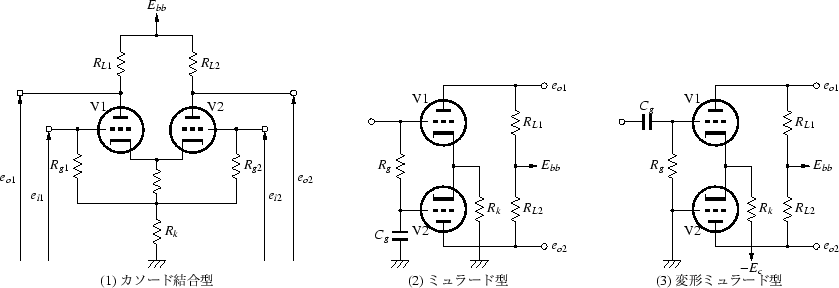

カソード結合型は,差動増幅回路の定電流源を高抵抗 Rk に変えたものです (図3.19 (1)参照). 差動増幅回路では,入力の約1/2がカソードに現われるため, 定電流源ではなく Rk を使用すると共通カソード電流がわずかながら変動し, 2つの出力は対称ではなくなります.

ミュラード型は,カソードの電位が高くなることを利用して, V1のグリッドと前段のプレートを直結にしたものです(図3.19 (2)). V2のグリッドを直流的にはV1のグリッドの電位とし, 交流的にはアースとするために, V2のグリッドは高抵抗 Rg を介してV1のグリッドに結び, また大容量の Cg でアースします. 良好な低域特性を得るためには, この時定数を他の段間の時定数よりもかなり大きくしておきます. ミュラード型のほうが回路が簡潔になるので, (1)のカソード結合型が使われることはまずありません.

ミュラード型では,カソード電圧 Ek は増幅にほとんど寄与しておらず, 大きな出力を得るためには,高い電源電圧 Ebb が必要になります. 電源電圧が低い場合,図3.19 (3)のように, 直結をあきらめて,グリッドの電位を0とし, カソード側を負の電源により引き込む回路を使うことがあります. この回路は,黒川達夫氏の作例[3,4]によく見られます.

| μ1eg1 | = | i1(rp1 + RL1) + (i1 + i2)Rk | (3.31) |

| μ2eg2 | = | i2(rp2 + RL2) + (i1 + i2)Rk | (3.32) |

| ei1 | = | eg1 + (i1 + i2)Rk | (3.33) |

| ei2 | = | eg2 + (i1 + i2)Rk | (3.34) |

| eo1 | = | - i1RL1 | (3.35) |

| eo2 | = | - i2RL2 | (3.36) |

| μ1{ei1 - (i1 + i2)Rk} | = | i1R1 + (i1 + i2)Rk | |

| μ2{ei2 - (i1 + i2)Rk} | = | i2R2 + (i1 + i2)Rk | |

| μ1ei1 | = | i1R1 + (1 + μ1)(i1 + i2)Rk | |

| μ2ei2 | = | i2R2 + (1 + μ2)(i1 + i2)Rk | |

| μ1ei1 | = | {R1 + (1 + μ1)Rk}i1 + (1 + μ1)Rki2 | |

| μ2ei2 | = | (1 + μ2)Rki1 + {R2 + (1 + μ2)Rk}i2 | |

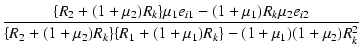

| {R2+(1+μ2)Rk}μ1ei1-(1+μ1)Rkμ2ei2 | |||

| = | {R2 + (1 + μ2)Rk}{R1 + (1 + μ1)Rk}i1 - (1 + μ1)(1 + μ2)Rk2i1 | ||

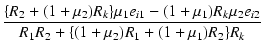

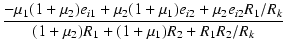

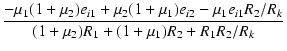

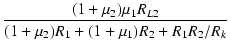

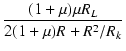

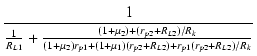

| i1 | = |  |

|

| = |  |

||

| = |  |

||

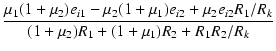

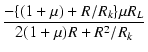

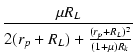

| i2 | = |  |

|

| eo1 | = |  RL1 RL1 |

(3.37) |

| eo2 | = |  RL2 RL2 |

(3.38) |

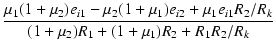

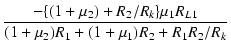

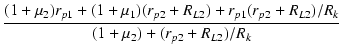

| A1 | = |  |

(3.39) |

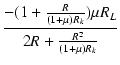

| A2 | = |  |

(3.40) |

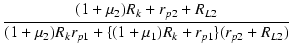

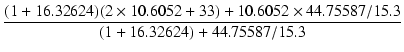

| A1 | = |  = =  = =  |

(3.41) |

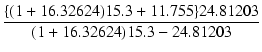

| A2 | = |  = =  |

(3.42) |

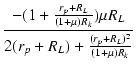

|

(3.43) |

ACバランスに関して,

「V2の負荷抵抗 RL2をV1の負荷抵抗 RL1 の 1 + m 倍して

両側のゲインを揃えればよい」,

という記述が多く見受けられますが,このようにしてもバランスは取れません.

RL2 を変えると,V1のゲインも変わってしまうからです.

正しいACバランスを得るためには,

| A1| = A2 を満たす RL2 と RL1 の関係を求めます.

| eo | = | i1RL1 | (3.45) |

| ek | = | (i2 + i3)Rk | (3.46) |

| eg1 | = | eg2 = - ek | (3.47) |

| eo + μ1eg1 | = | i2rp1 + (i2 + i3)Rk | (3.48) |

| μ2eg2 | = | i3(rp2 + RL2) + (i2 + i3)Rk | (3.49) |

| eo - μ1(i2 + i3)Rk | = | i2rp1 + (i2 + i3)Rk | |

| eo | = | {(1 + μ1)Rk + rp1}i2 + (1 + μ1)Rki3 | |

| - μ2(i2 + i3)Rk | = | i3(rp2 + RL2) + (i2 + i3)Rk | |

| 0 | = | (1 + μ2)Rki2 + {(1 + μ2)Rk + rp2 + RL2}i3 | |

| {(1 + μ2)Rk + rp2 + RL2}eo | = | [(1 + μ2)Rkrp1 + {(1 + μ1)Rk + rp1}(rp2 + RL2)]i2 | |

| i2 | = |  eo eo |

|

| = |  |

||

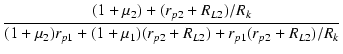

| Zo | = |  |

|

| = | RL1// |

(3.50) |

| R1 | = | R2 = 44.75587 [kΩ] | |

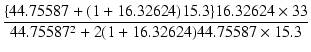

| A1 | = | -  = - 6.487483 = - 6.487483 |

|

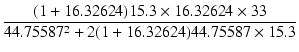

| A2 | = |  = 5.5504 = 5.5504 |

|

| Zo | = | 33// = 19.88694 [kΩ] = 19.88694 [kΩ] |

図3.22に, V1およびV2のプレートに 100 pF または 0.01 μF を 付加した場合の周波数特性を示します. 赤い線がV1側のゲイン, 青い線がV2側のゲインを表わしています. 実線は,V1,V2とも 100 pF を付加した場合, 破線は,V1に 100 pF, V2に 0.01 μF を付加した場合, 点線は,V1に 0.01 μF, V2に 100 pF を付加した場合, 一点鎖線は,V1,V2とも 0.01 μF を付加した場合です.

V1側に 220 pF, V2側に 200 pF を付加した場合の 周波数特性は図3.7のようになります. ごくわずかですが周波数特性にコブができていて, 差動増幅回路よりもクセがあることがわかります.

1 Mullard type phase inverter with 12AU7

2 .INCLUDE 12AU7.lib

3 .OPTIONS ITL1=200 ITL2=200

4 X1 1 2 3 12AU7

5 X2 4 5 3 12AU7

6 RK 3 0 15.3k

7 RL1 6 1 33k

8 RL2 6 4 33k

9 RG1 2 0 470k

10 RG2 5 0 470k

11 VI1 2 0 DC 94V

12 VI2 5 0 DC 94V

13 VBB 6 0 350V

14 .control

15 op

16 print v(1) v(3) v(1,3) v(2,3) v(4,3) v(5,3) i(vbb)

17 tf v(1) vi1

18 print all

19 tf v(4) vi1

20 print all

21 .endc

22 .END

1

2 Circuit: Mullard type phase inverter with 12AU7

3

4 v(1) = 2.421508e+02

5 v(3) = 1.000057e+02

6 v(1,3) = 1.421451e+02

7 v(2,3) = -6.00566e+00

8 v(4,3) = 1.421451e+02

9 v(5,3) = -6.00566e+00

10 i(vbb) = -6.53632e-03

11 transfer_function = -6.48748e+00

12 output_impedance_at_v(1) = 1.988694e+04

13 vi1#input_impedance = 4.700000e+05

14 transfer_function = 5.550397e+00

15 output_impedance_at_v(4) = 1.988694e+04

16 vi1#input_impedance = 4.700000e+05

例えば ei = 10 V の入力があった場合, カソード電圧は Ek = 104.9 V となり, V1のグリッド電圧は Eg1 = 94 + 10 - 104.9 = - 0.9 V となって, プレート電流が Ip1 = 5.29 mA 流れます. このときのプレート電圧は Ep1 = 70.6 V で, 対アースプレート電圧は Eo1 = 175.5 V になります. V2のグリッド電圧は Eg2 = 94 - 104.9 = - 10.9 V となって, プレート電流が Ip2 = 1.57 mA 流れます. このときのプレート電圧は Ep2 = 175.5 V で, 対アースプレート電圧は Eo2 = 298.3 V になります. プレート電流の合計は 5.29 + 1.57 = 6.86 mA となって, 無信号時のカソード電流 6.54 mA より増えています.

また,V1のロードラインと Eg = 0 の交点は,約 12 V なので, 尖頭値で 12 V までの入力を加えることができます.

伝達特性のグラフは,差動増幅回路と同様にRの関数 trans.diff を使用して作成できます.

> Ei <- seq(-20, 20, by=1) > z <- trans.diff(t12AU7, ei1=Ei, Ebb=350, Eg=94, RL1=33e3, Rk=15.3e3) > matplot(Ei, cbind(z$eo1, z$eo2), type="l", lty=1)図3.26のようなグラフが描かれます. 点線は,V1の出力を反転したもので,V1のゲインが大きいことがわかります.

| RL2 | = |  = 28.58815 [kΩ] = 28.58815 [kΩ] |

(3.51) |

| Rp2 | = |  = 40.03278 [kΩ] = 40.03278 [kΩ] |

(3.52) |

1 Mullard type phase inverter with 12AU7

2 .INCLUDE 12AU7.lib

3 X1 1 2 3 12AU7

4 X2 4 5 3 12AU7

5 RK 3 0 15.3k

6 RL1 6 1 33k

7 RL2 6 4 40.03278k

8 RG1 2 0 470k

9 RG2 5 0 470k

10 VI1 2 0 DC 94V AC 1V

11 VI2 5 0 DC 94V

12 VBB 6 0 350V

13 CC1 1 7 1u

14 CC2 4 8 1u

15 RG3 7 0 100k

16 RG4 8 0 100k

17 CS1 7 0 100p

18 CS2 8 0 100p

19 .control

20 ac dec 20 1 1Meg

21 print db(v(7)) db(v(8))

22 .endc

23 .END

プレート抵抗が増えたことによって,動作点が変化して, バイアスが浅くなっています.

伝達特性のグラフでは,プレートの電圧ではなく, 信号成分のみをとりだして(動作点のプレート電圧を引いて)描いています. 尖頭値で 50 V 程度までは両相の出力がよく揃っていますが, それ以上の出力を取り出すとバランスがくずれていきます.

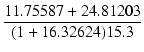

従来の方法で Rp2 を計算すると,

| m | = |  = =  = 0.1379445 = 0.1379445 |

|

| RL2 | = | RL1(1 + m) = 24.81203(1 + 16.32624) = 28.23471 [kΩ] | |

| Rp2 | = |  = 39.34313 [kΩ] = 39.34313 [kΩ] |

1 Mullard type phase inverter with 12AU7

2 .INCLUDE 12AU7.lib

3 X1 1 2 3 12AU7

4 X2 4 5 3 12AU7

5 RK 3 0 15.3k

6 RL1 6 1 33k

7 RL2 6 4 39.34313k

8 RG1 2 0 470k

9 RG2 5 0 470k

10 VI1 2 0 DC 94V AC 1V

11 VI2 5 0 DC 94V

12 VBB 6 0 350V

13 CC1 1 7 1u

14 CC2 4 8 1u

15 RG3 7 0 100k

16 RG4 8 0 100k

17 CS1 7 0 100p

18 CS2 8 0 100p

19 .control

20 ac dec 20 1 1Meg

21 print db(v(7)) db(v(8))

22 .endc

23 .END